残留DC測定(Residual DC Voltage Measurement)

液晶ディスプレイには、焼き付きという表示不良があります。これは表示されていた画像の影響が、次の画像に移った後も残ってしまう現象です。

例えば、長時間同じ画像を表示させておいて、画面を切り替えた場合などに起こりやすい現象です。

原因はハッキリとは解明されていませんが、長時間に渡って印加された電圧によって、

不純物イオンなどの存在する場所に偏りが出たり、不純物イオンが配向膜に取り込まれたりすることで、

印加した電圧から、偏ったイオンの電荷分だけ、印加電圧からズレてしまうことが原因だと言われています。

これを定量的に評価する方法が、残留DC測定です。

主な測定手法は2種類あります。

フリッカー消去法

最もポピュラーで、実際の現象をそのまま測定しているのが、フリッカー消去法です。これは原理は非常に簡単です。

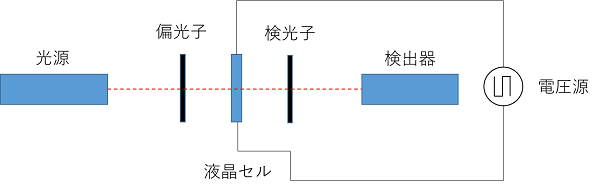

測定に必要な機材は、光源、偏光子と検光子、透過光強度を測定する検出器、電圧源(波形発生器)だけです。

通常、検出器としては、光電子増倍管やフォトディテクタのような光を電流や電圧に変換する素子と、

電流や電圧に変換された透過光強度を記録するためのオシロスコープを組み合わせて使用します。

測定手順は以下のようになります。

まず最初に、液晶に対して電圧を印加します。この時に印加する電圧を疲労波形と呼びます。

疲労波形を長時間印加することで電荷の偏りが誘起されてきます。

次に、矩形波を印加して、その時の液晶の透過光強度を測定します。

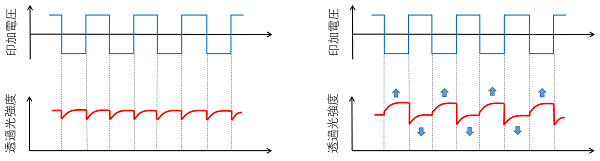

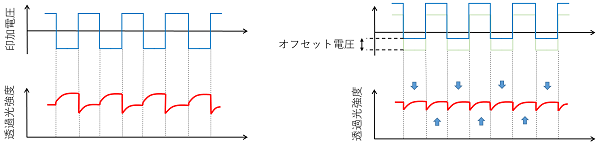

残留DC(電荷の偏り)が全くない場合、透過光強度は、矩形波の極性に関わらず一定になります。

しかし、残留DCがある場合、透過光強度には、矩形波の極性によって、差異が生じます。

この透過光強度の差異が現れた時、印加電圧の矩形波にオフセットとして直流電圧(DC電圧)を足します。

オフセット電圧を調整していくと、どこかで透過光強度が一定になるようになります。

つまり、電荷の偏りとオフセット電圧が打ち消されたと考えられる状態ができます。

この時のオフセット電圧を、残留DC電圧と呼び、焼き付きに繋がる特性値として評価をします。

この残留DC電圧は、疲労波形の印加時間に比例して大きくなっていきますが、

原因となっている電荷がすべて偏ってしまうと、それ以上は大きくならないので、最終的には収束していきます。

誘電吸収法

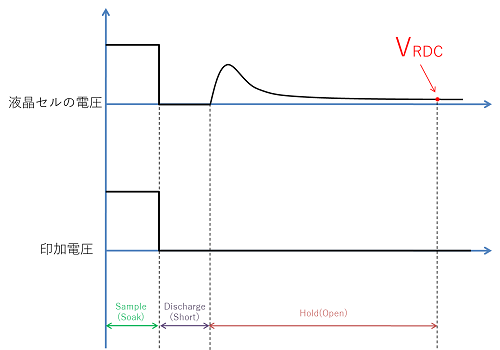

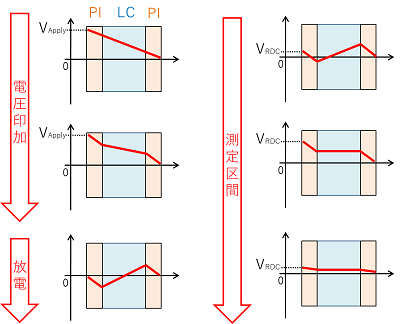

液晶セルを構成する配向膜や液晶の誘電吸収現象から残留DCを測定する手法があります。測定の概要を説明すると、液晶セルに直流電圧を印加して、一瞬だけ液晶セルの電極をショート(短絡)した後、

液晶セルの電極をオープン(開放)して、液晶セルに残る電圧の変化を測定するものです。

先ほど説明したフリッカー消去法が、実際に液晶セルの透過率を調べているのに比べて、

誘電吸収法は全くアプローチが異なっています。

誘電吸収法では、液晶セルが配向膜と液晶の積層構造であることに着目し、誘電緩和速度が異なることから、

残留DCが生じることに立脚しています。

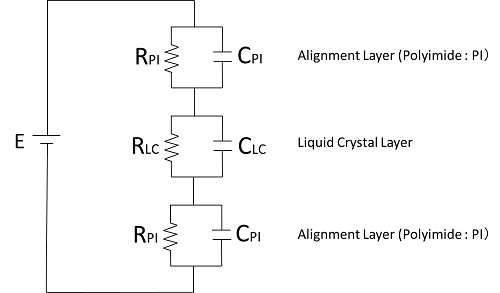

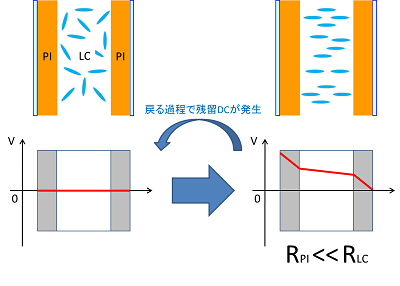

最も汎用な液晶セルを等価回路で書いたとすれば、下図のようになります。

配向膜はポリイミドが使われていることが多いため、PIと略して記載しています。

配向膜に使用される高分子膜は絶縁体です。

液晶も絶縁体の部類に入りますが、圧倒的に配向膜の抵抗値の方が高くなっています。

よって、液晶セルに十分な時間かけて電圧を印加した時、各層にかかる電圧(電位差)が、

必然的に配向膜にかかる電位差が大きくなり、液晶層にかかる電位差が小さくなります。

※電位差はオームの法則に従うので、抵抗値が大きいほうが電位差が大きくなる。

配向膜も液晶も、抵抗値は大きいので、一度生じた電位差を解消するためには、長時間の放電時間が必要になります。

したがって、一瞬入る放電過程では、両端の電位差を強制的にゼロにしますので、

各層内に生じた電位差が完全には解消されない状態で、両端の電位差がゼロになります。

この時、完全に解消しきれなかった電位差を、測定することで残留DCを測定しています。

一見すると、先ほどのフリッカー消去法と全く違うように見えますが、

誘電吸収法で測定した残留DCと、フリッカー消去法で測定した残留DCは相関があることが確かめられています。

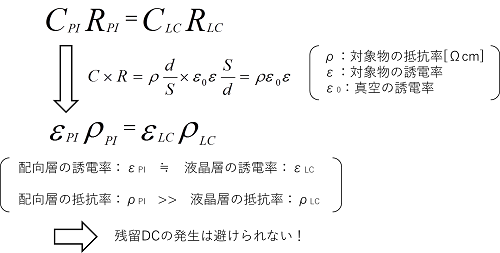

さて、誘電吸収法の概要が分かったところで、誘電吸収法の原理から、残留DCをゼロにする条件について書きましょう。

細かい数式が増えるので、そのあたり説明は飛ばして、結論だけを書けば、

「配向層の誘電率と抵抗率の積が、液晶層の誘電率と抵抗率の積と一致すれば良い」となります。

この条件について考えてみましょう。

配向層と液晶層の誘電率は、ほとんど同じくらいのオーダーです。大きく乖離することは材料の特性上ありません。

問題は抵抗率です。先に述べたように、圧倒的に配向層の抵抗率は、液晶層の抵抗率に比べて大きいのです。

つまり、先ほどの条件は、満たすことができない条件と言え、残留DCは必ず発生する事になります。

残留DCが必ず発生するんなら、配向層と液晶層の組み合わせはなんでもいい。というわけではありません。

できる限り、配向層の誘電率と抵抗率の積と、液晶層の誘電率と抵抗率の積が、近いほど残留DCは小さいのです。

先に説明した通り、抵抗率の乖離が大きいので、できるだけ抵抗率を近づけるようにしたいのですが、

液晶層の抵抗率を非常に大きくしていくのは難しいので、配向層の抵抗率を下げるように考えるのが一般的です。